芯片的制造工艺常常用90nm、65nm、40nm、28nm、22nm、14nm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm制造工艺。现在的CPU内集成了以亿为单位的晶体管,这种晶体管由源极、漏极和位于他们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流通断的作用。

而所谓的 nm其实指的是,CPU的上形成的互补氧化物金属半导体场效应晶体管栅极的宽度,也被称为栅长。栅长越短,则可以在相同尺寸的硅片上集成更多的晶体管——Intel曾经宣称将栅长从130nm减小到90nm时,晶体管所占得面积将减小一半;在芯片晶体管集成度相当的情况下,使用更先进的制造工艺,芯片的面积和功耗就越小,成本也越低。

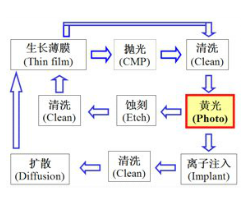

栅长可以分为光刻栅长和实际栅长,光刻栅长则是由光刻技术所决定的。由于在光刻中光存在衍射现象以及芯片制造中还要经历离子注入、蚀刻、等离子冲洗、热处理等步骤,因此会导致光刻栅长和实际栅长不一致的情况。另外,同样的制程工艺下,实际栅长也会不一样,比如虽然三星也推出了14nm制程工艺的芯片,但其芯片的实际栅长和Intel的14nm制程芯片的实际栅长依然有一定差距。

为什么说7nm是物理极限?

缩短晶体管栅极的长度可以使CPU集成更多的晶体管或者有效减少晶体管的面积和功耗,并削减CPU的硅片成本。正因如此,CPU生产厂商不遗余力地减小晶体管栅极宽度,以提高在单位面积上所集成的晶体管数量。不过这种做法也会使电子移动的距离缩短,容易导致晶体管内部电子自发通过晶体管通道的硅底板进行的从负极流向正极的运动,也就是漏电。而且随着芯片中晶体管数量增加,原本仅数个原子层厚的二氧化硅绝缘层会变得更薄进而导致泄漏更多电子,随后泄漏的电流又增加了芯片额外的功耗。

为了解决漏电问题,Intel、IBM等公司可谓八仙过海,各显神通。比如Intel在其制造工艺中融合了高介电薄膜和金属门集成电路以解决漏电问题;IBM开发出SOI技术——在在源极和漏极埋下一层强电介质膜来解决漏电问题;此外,还有鳍式场效电晶体技术——借由增加绝缘层的表面积来增加电容值,降低漏电流以达到防止发生电子跃迁的目的......

上述做法在栅长大于7nm的时候一定程度上能有效解决漏电问题。不过,在采用现有芯片材料的基础上,晶体管栅长一旦低于7nm,晶体管中的电子就很容易产生隧穿效应,为芯片的制造带来巨大的挑战。针对这一问题,寻找新的材料来替代硅制作7nm以下的晶体管则是一个有效的解决之法。

1nm制程晶体管还处于实验室阶段, 或许近在咫尺, 举步之遥....

碳纳米管和近年来非常火爆的石墨烯有一定联系,零维富勒烯、一维碳纳米管、二维石墨烯都属于碳纳米材料家族,并且彼此之间满足一定条件后可以在形式上转化。碳纳米管是一种具有特殊结构的一维材料,它的径向尺寸可达到纳米级,轴向尺寸为微米级,管的两端一般都封口,因此它有很大的强度,同时巨大的长径比有望使其制作成韧性极好的碳纤维。

碳纳米管和石墨烯在电学和力学等方面有着相似的性质,有较好的导电性、力学性能和导热性,这使碳纳米管复合材料在超级电容器、太阳能电池、显示器、生物检测、燃料电池等方面有着良好的应用前景。此外,掺杂一些改性剂的碳纳米管复合材料也受到人们的广泛关注,例如在石墨烯/碳纳米管复合电极上添加CdTe量子点制作光电开关、掺杂金属颗粒制作场致发射装置。本次外媒报道的劳伦斯伯克利国家实验室将现有最精尖的晶体管制程从14nm缩减到了1nm,其晶体管就是由碳纳米管掺杂二硫化钼制作而成。不过这一技术成果仅仅处于实验室技术突破的阶段,目前还没有商业化量产的能力。至于该项技术将来是否会成为主流商用技术,还有待时间检验。

CPU制造工艺分类

制造工艺

生产CPU与GPU等芯片的材料是半导体,现阶段主要的材料是硅Si,这是一种非金属元素,从化学的角度来看,由于它处于元素周期表中金属元素区与非金属元素区的交界处,所以具有半导体的性质,适合于制造各种微小的晶体管,是目前最适宜于制造现代大规模集成电路的材料之一。在硅提纯的过程中,原材料硅将被熔化,并放进一个巨大的石英熔炉。这时向熔炉里放入一颗晶种,以便硅晶体围着这颗晶种生长,直到形成一个几近完美的单晶硅。以往的硅锭的直径大都是200毫米,而CPU或GPU厂商正在增加300毫米晶圆的生产。

切割晶圆

为加工新的一层电路,再次生长硅氧化物,然后沉积一层多晶硅,涂敷光阻物质,重复影印、蚀刻过程,得到含多晶硅和硅氧化物的沟槽结构。重复多遍,形成一个3D的结构,这才是最终的CPU与GPU的核心。每几层中间都要填上金属作为导体。

封装

这时的CPU或GPU是一块块晶圆,它还不能直接被用户使用,必须将它封入一个陶瓷的或塑料的封壳中,这样它就可以很容易地装在一块电路板上了。封装结构各有不同,但越高级的处理器封装也越复杂,新的封装往往能带来芯片电气性能和稳定性的提升,并能间接地为主频的提升提供坚实可靠的基础。

多次测试

测试是一个处理器制造的重要环节,也是一块处理器出厂前必要的考验。这一步将测试晶圆的电气性能,以检查是否出了什么差错,以及这些差错出现在哪个步骤。

晶圆专业术语

Acceptor - An element, such as boron, indium, and gallium used to create a free hole in a semiconductor. The acceptor atoms are required to have one less valence electron than the semiconductor.

受主 - 一种用来在半导体中形成空穴的元素,比如硼、铟和镓。受主原子必须比半导体元素少一价电子

Alignment Precision - Displacement of patterns that occurs during the photolithography process.

套准精度 - 在光刻工艺中转移图形的精度。

Anisotropic - A process of etching that has very little or no undercutting

各向异性 - 在蚀刻过程中,只做少量或不做侧向凹刻。

Area Contamination - Any foreign particles or material that are found on the surface of a wafer. This is viewed as discolored or smudged, and it is the result of stains, fingerprints, water spots, etc.

沾污区域 - 任何在晶圆片表面的外来粒子或物质。由沾污、手印和水滴产生的污染。

Azimuth, in Ellipsometry - The angle measured between the plane of incidence and the major axis of the ellipse.

椭圆方位角 - 测量入射面和主晶轴之间的角度。

Backside - The bottom surface of a silicon wafer. (Note: This term is not preferred; instead, use ‘back surface’.)

背面 - 晶圆片的底部表面。(注:不推荐该术语,建议使用“背部表面”)

Base Silicon Layer - The silicon wafer that is located underneath the insulator layer, which supports the silicon film on top of the wafer.

底部硅层 - 在绝缘层下部的晶圆片,是顶部硅层的基础。

Bipolar - Transistors that are able to use both holes and electrons as charge carriers.

双极晶体管 - 能够采用空穴和电子传导电荷的晶体管。

Bonded Wafers - Two silicon wafers that have been bonded together by silicon dioxide, which acts as an insulating layer.

绑定晶圆片 - 两个晶圆片通过二氧化硅层结合到一起,作为绝缘层。

Bonding Interface - The area where the bonding of two wafers occurs.

绑定面 - 两个晶圆片结合的接触区。

Buried Layer - A path of low resistance for a current moving in a device. Many of these dopants are antimony and arsenic.

埋层 - 为了电路电流流动而形成的低电阻路径,搀杂剂是锑和砷。

Buried Oxide Layer (BOX) - The layer that insulates between the two wafers.

氧化埋层(BOX) - 在两个晶圆片间的绝缘层。

Carrier - Valence holes and conduction electrons that are capable of carrying a charge through a solid surface in a silicon wafer.

载流子 - 晶圆片中用来传导电流的空穴或电子。

Chemical-Mechanical Polish (CMP) - A process of flattening and polishing wafers that utilizes both chemical removal and mechanical buffing. It is used during the fabrication process.

化学-机械抛光(CMP) - 平整和抛光晶圆片的工艺,采用化学移除和机械抛光两种方式。此工艺在前道工艺中使用。

Chuck Mark - A mark found on either surface of a wafer, caused by either a robotic end effector, a chuck, or a wand.

卡盘痕迹 - 在晶圆片任意表面发现的由机械手、卡盘或托盘造成的痕迹。

Cleavage Plane - A fracture plane that is preferred.

解理面 - 破裂面

Crack - A mark found on a wafer that is greater than 0.25 mm in length.

裂纹 - 长度大于0.25毫米的晶圆片表面微痕。

Crater - Visible under diffused illumination, a surface imperfection on a wafer that can be distinguished individually.

微坑 - 在扩散照明下可见的,晶圆片表面可区分的缺陷。

Conductivity (electrical) - A measurement of how easily charge carriers can flow throughout a material.

传导性(电学方面) - 一种关于载流子通过物质难易度的测量指标 。

Conductivity Type - The type of charge carriers in a wafer, such as “N-type” and “P-type”.

导电类型 - 晶圆片中载流子的类型,N型和P型。

Contaminant, Particulate (see light point defect)

污染微粒 (参见光点缺陷)

Contamination Area - An area that contains particles that can negatively affect the characteristics of a silicon wafer.

沾污区域 - 部分晶圆片区域被颗粒沾污,造成不利特性影响。

Contamination Particulate - Particles found on the surface of a silicon wafer.

沾污颗粒 - 晶圆片表面上的颗粒。

Crystal Defect - Parts of the crystal that contain vacancies and dislocations that can have an impact on a circuit’s electrical performance.

晶体缺陷 - 部分晶体包含的、会影响电路性能的空隙和层错。

Crystal Indices (see Miller indices)

晶体指数 (参见米勒指数)

Depletion Layer - A region on a wafer that contains an electrical field that sweeps out charge carriers.

耗尽层 - 晶圆片上的电场区域,此区域排除载流子。

Dimple - A concave depression found on the surface of a wafer that is visible to the eye under the correct lighting conditions.

表面起伏 - 在合适的光线下通过肉眼可以发现的晶圆片表面凹陷。

Donor - A contaminate that has donated extra “free” electrons, thus making a wafer “N-Type”.

施主 - 可提供“自由”电子的搀杂物,使晶圆片呈现为N型。

Dopant - An element that contributes an electron or a hole to the conduction process, thus altering the conductivity. Dopants for silicon wafers are found in Groups III and V of the Periodic Table of the Elements.

搀杂剂 - 可以为传导过程提供电子或空穴的元素,此元素可以改变传导特性。晶圆片搀杂 剂可以在元素周期表的III 和 V族元素中发现。

Doping - The process of the donation of an electron or hole to the conduction process by a dopant.

掺杂 - 把搀杂剂掺入半导体,通常通过扩散或离子注入工艺实现。

Edge Chip and Indent - An edge imperfection that is greater than 0.25 mm.

芯片边缘和缩进 - 晶片中不完整的边缘部分超过0.25毫米。

Edge Exclusion Area - The area located between the fixed quality area and the periphery of a wafer. (This varies according to the dimensions of the wafer.)

边缘排除区域 - 位于质量保证区和晶圆片外围之间的区域。(根据晶圆片的尺寸不同而有所不同。)

Edge Exclusion, Nominal (EE) - The distance between the fixed quality area and the periphery of a wafer.

名义上边缘排除(EE) - 质量保证区和晶圆片外围之间的距离。

Edge Profile - The edges of two bonded wafers that have been shaped either chemically or mechanically.

边缘轮廓 - 通过化学或机械方法连接起来的两个晶圆片边缘。

Etch - A process of chemical reactions or physical removal to rid the wafer of excess materials.

蚀刻 - 通过化学反应或物理方法去除晶圆片的多余物质。

Fixed Quality Area (FQA) - The area that is most central on a wafer surface.

质量保证区(FQA) - 晶圆片表面中央的大部分。

Flat - A section of the perimeter of a wafer that has been removed for wafer orientation purposes.

平边 - 晶圆片圆周上的一个小平面,作为晶向定位的依据。

Flat Diameter - The measurement from the center of the flat through the center of the wafer to the opposite edge of the wafer. (Perpendicular to the flat)

平口直径 - 由小平面的中心通过晶圆片中心到对面边缘的直线距离。

Four-Point Probe - Test equipment used to test resistivity of wafers.

四探针 - 测量半导体晶片表面电阻的设备。

Furnace and Thermal Processes - Equipment with a temperature gauge used for processing wafers. A constant temperature is required for the process.

炉管和热处理 - 温度测量的工艺设备,具有恒定的处理温度。

Front Side - The top side of a silicon wafer. (This term is not preferred; use front surface instead.)

正面 - 晶圆片的顶部表面(此术语不推荐,建议使用“前部表面”)。

Goniometer - An instrument used in measuring angles.

角度计 - 用来测量角度的设备。

Gradient, Resistivity (not preferred; see resistivity variation)

电阻梯度 (不推荐使用,参见“电阻变化”)

Groove - A scratch that was not completely polished out.

凹槽 - 没有被完全清除的擦伤。

Hand Scribe Mark - A marking that is hand scratched onto the back surface of a wafer for identification purposes.

手工印记 - 为区分不同的晶圆片而手工在背面做出的标记。

Haze - A mass concentration of surface imperfections, often giving a hazy appearance to the wafer.

雾度 - 晶圆片表面大量的缺陷,常常表现为晶圆片表面呈雾状。

Hole - Similar to a positive charge, this is caused by the absence of a valence electron.

空穴 - 和正电荷类似,是由缺少价电子引起的。

Ingot - A cylindrical solid made of polycrystalline or single crystal silicon from which wafers are cut.

晶锭 - 由多晶或单晶形成的圆柱体,晶圆片由此切割而成。

Laser Light-Scattering Event - A signal pulse that locates surface imperfections on a wafer.

激光散射 - 由晶圆片表面缺陷引起的脉冲信号。

Lay - The main direction of surface texture on a wafer.

层 - 晶圆片表面结构的主要方向。

Light Point Defect (LPD) (Not preferred; see localized light-scatterer)

光点缺陷(LPD) (不推荐使用,参见“局部光散射”)

Lithography - The process used to transfer patterns onto wafers.

光刻 - 从掩膜到圆片转移的过程。

Localized Light-Scatterer - One feature on the surface of a wafer, such as a pit or a scratch that scatters light. It is also called a light point defect.

局部光散射 - 晶圆片表面特征,例如小坑或擦伤导致光线散射,也称为光点缺陷。

Lot - Wafers of similar sizes and characteristics placed together in a shipment.

批次 - 具有相似尺寸和特性的晶圆片一并放置在一个载片器内。

Majority Carrier - A carrier, either a hole or an electron that is dominant in a specific region, such as electrons in an N-Type area.

多数载流子 - 一种载流子,在半导体材料中起支配作用的空穴或电子,例如在N型中是电子。

Mechanical Test Wafer - A silicon wafer used for testing purposes.

机械测试晶圆片 - 用于测试的晶圆片。

Microroughness - Surface roughness with spacing between the impurities with a measurement of less than 100 μm.

微粗糙 - 小于100微米的表面粗糙部分。

Miller Indices, of a Crystallographic Plane - A system that utilizes three numbers to identify plan orientation in a crystal.

Miller索指数 - 三个整数,用于确定某个并行面。这些整数是来自相同系统的基本向量。

Minimal Conditions or Dimensions - The allowable conditions for determining whether or not a wafer is considered acceptable.

最小条件或方向 - 确定晶圆片是否合格的允许条件。

Minority Carrier - A carrier, either a hole or an electron that is not dominant in a specific region, such as electrons in a P-Type area.

少数载流子 - 在半导体材料中不起支配作用的移动电荷,在P型中是电子,在N型中是空穴。

Mound - A raised defect on the surface of a wafer measuring more than 0.25 mm.

堆垛 - 晶圆片表面超过0.25毫米的缺陷。

Notch - An indent on the edge of a wafer used for orientation purposes.

凹槽 - 晶圆片边缘上用于晶向定位的小凹槽。

Orange Peel - A roughened surface that is visible to the unaided eye.

桔皮 - 可以用肉眼看到的粗糙表面

Orthogonal Misorientation -

直角定向误差 -

Particle - A small piece of material found on a wafer that is not connected with it.

颗粒 - 晶圆片上的细小物质。

Particle Counting - Wafers that are used to test tools for particle contamination.

颗粒计算 - 用来测试晶圆片颗粒污染的测试工具。

Particulate Contamination - Particles found on the surface of a wafer. They appear as bright points when a collineated light is shined on the wafer.

颗粒污染 - 晶圆片表面的颗粒。

Pit - A non-removable imperfection found on the surface of a wafer.

深坑 - 一种晶圆片表面无法消除的缺陷。

Point Defect - A crystal defect that is an impurity, such as a lattice vacancy or an interstitial atom.

点缺陷 - 不纯净的晶缺陷,例如格子空缺或原子空隙。

Preferential Etch -

优先蚀刻 -

Premium Wafer - A wafer that can be used for particle counting, measuring pattern resolution in the photolithography process, and metal contamination monitoring. This wafer has very strict specifications for a specific usage, but looser specifications than the prime wafer.

测试晶圆片 - 影印过程中用于颗粒计算、测量溶解度和检测金属污染的晶圆片。对于具体应用该晶圆片有严格的要求,但是要比主晶圆片要求宽松些。

Primary Orientation Flat - The longest flat found on the wafer.

主定位边 - 晶圆片上最长的定位边。

Process Test Wafer - A wafer that can be used for processes as well as area cleanliness.

加工测试晶圆片 - 用于区域清洁过程中的晶圆片。

Profilometer - A tool that is used for measuring surface topography.

表面形貌剂 - 一种用来测量晶圆片表面形貌的工具。

Resistivity (Electrical) - The amount of difficulty that charged carriers have in moving throughout material.

电阻率(电学方面) - 材料反抗或对抗电荷在其中通过的一种物理特性。

Required - The minimum specifications needed by the customer when ordering wafers.

必需 - 订购晶圆片时客户必须达到的最小规格。

Roughness - The texture found on the surface of the wafer that is spaced very closely together.

粗糙度 - 晶圆片表面间隙很小的纹理。

Saw Marks - Surface irregularities

锯痕 - 表面不规则。

Scan Direction - In the flatness calculation, the direction of the subsites.

扫描方向 - 平整度测量中,局部平面的方向。

Scanner Site Flatness -

局部平整度扫描仪 -

Scratch - A mark that is found on the wafer surface.

擦伤 - 晶圆片表面的痕迹。

Secondary Flat - A flat that is smaller than the primary orientation flat. The position of this flat determines what type the wafer is, and also the orientation of the wafer.

第二定位边 - 比主定位边小的定位边,它的位置决定了晶圆片的类型和晶向。

Shape -

形状 -

Site - An area on the front surface of the wafer that has sides parallel and perpendicular to the primary orientation flat. (This area is rectangular in shape)

局部表面 - 晶圆片前面上平行或垂直于主定位边方向的区域。

Site Array - a neighboring set of sites

局部表面系列 - 一系列的相关局部表面。

Site Flatness -

局部平整 -

Slip - A defect pattern of small ridges found on the surface of the wafer.

划伤 - 晶圆片表面上的小皱造成的缺陷。

Smudge - A defect or contamination found on the wafer caused by fingerprints.

污迹 - 晶圆片上指纹造成的缺陷或污染。

Sori -

Striation - Defects or contaminations found in the shape of a helix.

条痕 - 螺纹上的缺陷或污染。

Subsite, of a Site - An area found within the site, also rectangular. The center of the subsite must be located within the original site.

局部子表面 - 局部表面内的区域,也是矩形的。子站中心必须位于原始站点内部。

Surface Texture - Variations found on the real surface of the wafer that deviate from the reference surface.

表面纹理 - 晶圆片实际面与参考面的差异情况。

Test Wafer - A silicon wafer that is used in manufacturing for monitoring and testing purposes.

测试晶圆片 - 用于生产中监测和测试的晶圆片。

Thickness of Top Silicon Film - The distance found between the face of the top silicon film and the surface of the oxide layer.

顶部硅膜厚度 - 顶部硅层表面和氧化层表面间的距离。

Top Silicon Film - The layer of silicon on which semiconductor devices are placed. This is located on top of the insulating layer.

顶部硅膜 - 生产半导体电路的硅层,位于绝缘层顶部。

Total Indicator Reading (TIR) - The smallest distance between planes on the surface of the wafer.

总计指示剂数(TIR) - 晶圆片表面位面间的最短距离。

Virgin Test Wafer - A wafer that has not been used in manufacturing or other processes.

原始测试晶圆片 - 还没有用于生产或其他流程中的晶圆片。

Void - The lack of any sort of bond (particularly a chemical bond) at the site of bonding.

无效 - 在应该绑定的地方没有绑定(特别是化学绑定)。

Waves - Curves and contours found on the surface of the wafer that can be seen by the naked eye.

波浪 - 晶圆片表面通过肉眼能发现的弯曲和曲线。

Waviness - Widely spaced imperfections on the surface of a wafer.

波纹 - 晶圆片表面经常出现的缺陷。